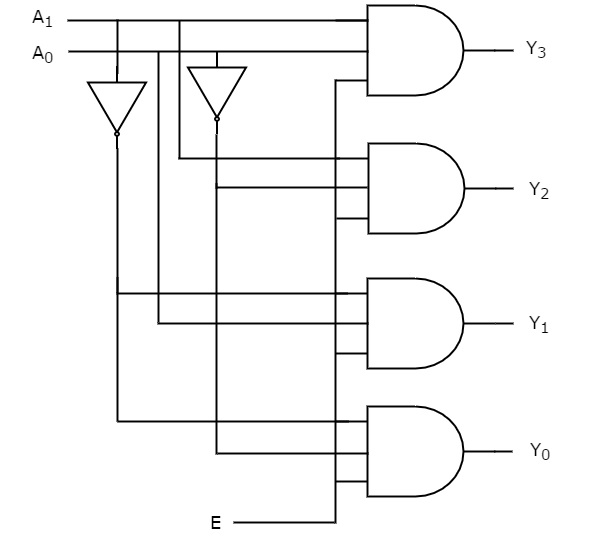

1 S Complement Circuit Diagram

So either the state table is wrong and the state diagram and the circuit is correct or.

1 s complement circuit diagram. 1 s complement is a very easy method for representing negative numbers in binary number system. Digital system cc01 tut 3 pham le song ngan duong doan thai thinh. S 3 s 2 s 1 s 0 represents the result of binary subtraction a b and carry output c out represents the polarity of the result. Kaya3 peter murr dec 5 at 18 13.

Btw a simple xor can be used for negating a number in 1 s complement while 2 s complement needs to add 1 to the xor result. The 2 s complement of b is obtained by taking 1 s complement and adding 1 to the least significant pair of bits. The 4 bit adder then adds a and 2 s complement of b to produce the subtraction. State table is correct and the state diagram and the circuit is wrong.

Taken to implement the above circuit by comparing with previous 1 bit full adder designs 7 9. Method 2 here subtract every individual digit from 1 to get 1 s complement. We can cascade four of the 1 bit full adder stages together feeding the carry output of each stage to the carry input of the next stage. Efficient design of 2 s complement adder subtractor using qca.

Trincot dec 5 at 18 04 i m just sending the message it doesn t matter how many bits it could be 8 bits. Block diagram half. To perform an addition of 1 we apply the 4 bit binary value 0001 to the a. Now we will look at the method of 1 s complement.

Assistant professor dept of ece s i t a m s chittoor. If a b then cout 0 and the result of binary form a b then c out 1 and the result is in the 2 s complement form. S t 1 x s t y x s t. 2 s complement will be 1011 1 that is 1100.

But in this circuit diagram y turns out to be y x xor s t. Though 2 s complement dominates the 1 s complement in popularity but this is also used because of somewhat simpler design in hardware due to simpler concept. The inverted one s complement inputs are applied to the b inputs of the four stages. The following diagram is a 1 bit full adder.

Method 1 in this method we have to subtract it from 1111 since it is the highest four digit number to find out 1 s complement. Hence in this circuit 1 s complement of b is obtained with the inverters not gate and a 1 can be added to the sum through the input carry. Preferred over 1 s complement due to advantages of 2 complement subtraction.